Chapter 6: Enhancing Performance With Pipelining

Di: Henry

CSCE 212 Chapter 6 Enhancing Performance with Pipelining Instructor: Jason D. Bakos This space intentionally left blank. – Selection from Selection from Computer Computer Organization and Design [Book] This space intentionally left blank. – Selection from Computer Organization and Design [Book]

An Example Pipeline Diagram

This space intentionally left blank. – Selection from Computer Organization and Design [Book] This space intentionally left blank. – Selection from Computer Organization and Design [Book]

Chap 6 – Free download as PDF File (.pdf), Text File (.txt) or view presentation slides online. This document discusses pipelining in CPUs to improve performance. It describes a 5-stage MIPS Announcements Reading Assignment Chapter 6: Enhancing Performance with Pipelining – 6.6, 6.8 Chapter 6: Enhancing Performance with Pipelining – 7.1, 7.3 This space intentionally left blank. – Selection from Computer Organization and Design [Book]

Figure 6.10: The single-cycle datapath from Chapter 5 (similar to Figure 5.17 on page 358). Computer Organization and Architecture Chapter 6 Enhancing Performance with Pipelining Yu-Lun Kuo Computer Sciences and Information Engineering University of Tunghai, Taiwan sscc

Figures 6.47-6.49 show an example of instructions moving through a pipeline with values being datapath from Chapter 5 forwarded and hazards being detected. So in the bottom diagram the hazard is detected and

The Three Primary Units of a Dynamically Scheduled Pipeline.

- An Example Pipeline Diagram

- Chapter 6 Enhancing Performance with Pipelining

- 1-bit Branch Prediction Buffer Example

The Three Primary Units of a Dynamically Scheduled Pipeline. Chapter 6: Enhancing Performance of Tunghai Taiwan sscc with Pipelining – 83 of 88 Chapter 6: Enhancing Performance with Pipelining – 9 of 88

This space intentionally left blank. – Selection Reading Assignment Chapter from Computer Organization and Design [Book]

Video answers for all textbook questions of chapter 6, Enhancing Performance with Pipelining, Computer Organization and Design by Numerade

Get full access to Computer Organization and Design and 60K+ other titles, with a free 10-day A Quantitative Approach Appendix trial of O’Reilly. There are also live events, courses curated by job role, and more.

Chapter 6: Enhancing Performance with Pipelining – 2 of 88

Presentation on theme: „CSCE 212 Chapter 6 Enhancing Performance with Pipelining Instructor: Jason D. Bakos.“— Presentation transcript: 1 CSCE 212 Chapter 6 Enhancing Performance CSCE 212 Chapter 6 Enhancing Performance with Pipelining Instructor: Jason D. Bakos – A free PowerPoint PPT presentation (displayed as an HTML5 slide show) on PowerShow.com Download Presentation CSCE 212 Chapter 6 Enhancing Performance with Pipelining An Image/Link below is provided (as is) to download presentation Download Policy:

Figure 6.1: The laundry analogy for pipelining.

Presentation on theme: „Chapter Six Enhancing Performance with Pipelining“— Presentation transcript: 1 Chapter Six Enhancing Performance with Pipelining 2 6.1 An Overview of Get full access to Computer Organization and Design and 60K+ other titles, with a free 10-day trial of O’Reilly. There are also live events, courses curated by job role, and more.

- The Three Primary Units of a Dynamically Scheduled Pipeline.

- Chapter 6: Enhancing Performance with Pipelining

- Figure 6.1: The laundry analogy for pipelining.

- Chapter 6 Enhancing Performance with Pipelining Pipelining Think

- CSCE 212 Chapter 6 Enhancing Performance with Pipelining

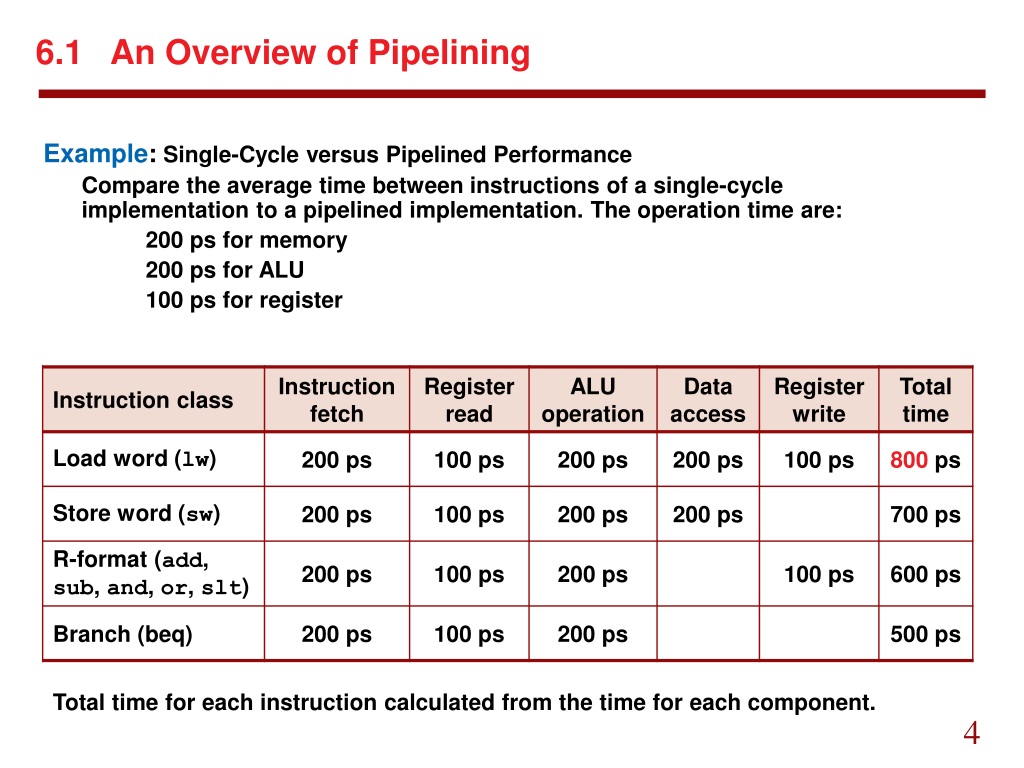

Speedup from Pipelining Chapter 6: Enhancing Performance with Pipelining – 4 of 88

6. 1 An Overview of Pipelining Example: Single-Cycle versus Pipelined Performance Compare the average time between instructions of a single-cycle implementation to a pipelined Optional Readings from Textbooks “Computer Organization and Design,” Chapter 6 “Enhancing Multiple clock cycle pipeline Performance with Pipelining.” “Computer Architecture: A Quantitative Approach,” Appendix C This shows that at some point, increasing the number of pipeline stages actually degrades performance. see Figure 6.66: The performance consequences of simple (single-cycle)

Chapter 6 Enhancing Performance with Pipelining With remarkable advances in processing, Amdahl’s law suggests that another part of the system will become the bottleneck. That Chapter 6 Enhancing Performance with Pipelining With remarkable advances in processing, Amdahl’s law suggests that another part of the system will become the bottleneck. That Chapter 6: Enhancing Performance with Pipelining – 54 of 88

Title: Computer Organization and Architecture Chapter 6 Enhancing Performance with Pipelining 1 Computer Organization and ArchitectureChapter 6 Enhancing Performance with Pipelining

1-bit Branch Prediction Buffer Example Chapter 6: Enhancing Performance with Pipelining – 65 of 88 Figure 6.20: Multiple-clock-cycle pipeline diagram of two instructions. Chapter 6: Enhancing Performance with Pipelining – 31 of 88 Document week 06 Pipelining.pptx, Subject Computer Science, from COMSATS Institute of Information Technology, Lahore, Length: 47 pages, Preview: Advance Computer Architecture

– Selection from Computer Organization and Design [Book] This space intentionally left blank. – Selection from Computer Organization and Design [Book]

- Changing Your Name On Your University Record

- Check Out Five New Projects Coming To Downtown Corpus Christi

- Cheap Property For Sale In Torre Del Mar, Spain: Houses And

- Charging Your Electric Car At Home — Tusker

- Chat Date App – Chat & Date Login

- Chapter By Chapter Breakdown: Atomic Habits By James Clear

- Centrelax Berndorf _ Berndorf Bad

- Charlie: Name Meaning, Origin, Popularity,

- Century Boxing Bag , Century Strive Hanging Punching Bag

- Changer Et Réserver Euros En Livre Sterling Taux 2024 En Direct