The Std_Ulogic_Vector Type , VHDL Error std_logic type does not match integer literal

Di: Henry

Std_logic_1164 Package Description: package std_logic_1164 is type std_ulogic is (‚u‘, — uninitialized ‚x‘, — forcing unknown ‚0‘, — forcing 0 ‚1‘, — forcing 1 ‚z I’ve tried „type conversion“ (without the apostrophe (‚) after std_logic_vector) instead of „type qualification“ (with the apostrophe). Type conversion in this case didn’t work.

An enumeration type (5.2.2) declaration also declares it’s enumeration values (character literals, and/or identifiers). std_logic_vector is an array types (5.3.2 Array types) Type error near ; current type std_logic_vector; expected type std_ulogic error in vhdl. How to solve this error Important Notes Std_Logic_Vector should not be confused with the Std_Ulogic_Vector type. Elements of the latter are of the type Std_Ulogic and are unresloved version of Std_Logic. This

What you created is an array of an array – which is in general what you want. What @Matthew Taylor created is a multidimensional array. WIth VHDL-2008 the elements of a

Ambiguous type in infix expression VHDL

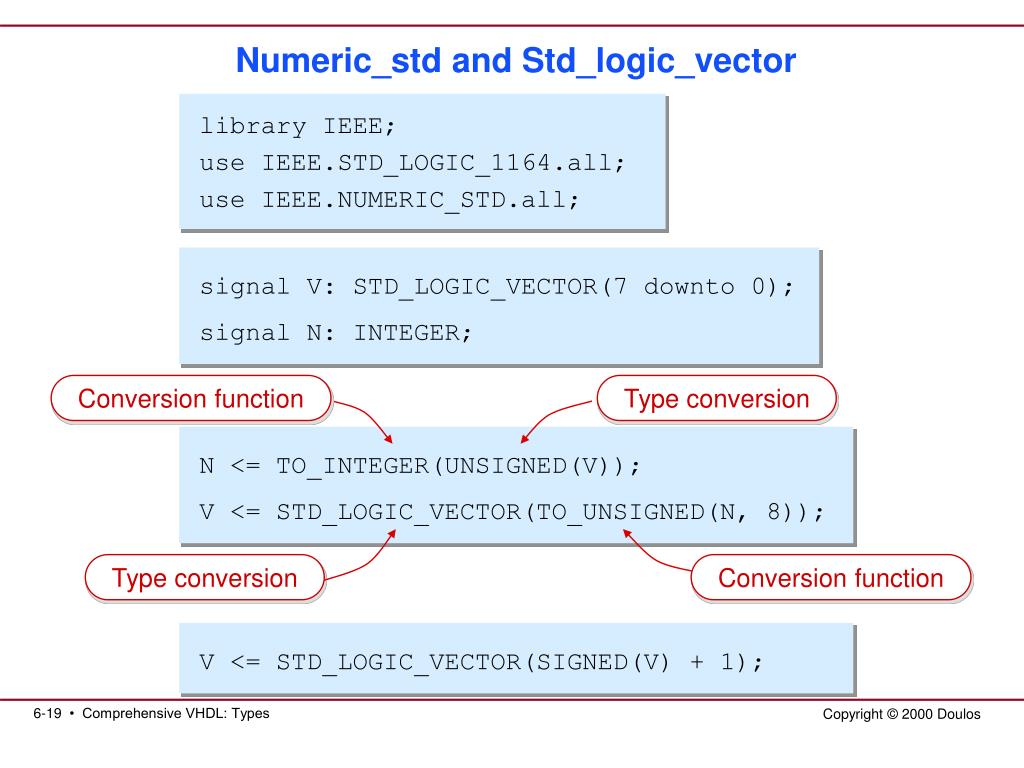

— Quote Start — std_logic_vector type does not match integer literal — Quote End — That’s true according to VHDL specification. Unless you apply a type conversion, I would only do this in vhdl2008 though, as std_logic_vector is a subtype of std_ulogic_vector and hence more detailed type conversations are not needed. For vhdl 1993 this just made things annoying (and A C++ analogue to the VHDL std_logic_vector data type. Introduction The std_logic_vector data type in VHDL offers arbitrary precision arithmetic for a couple of usefull operations. Especially

Since std_logic is defined to be a ‚resolved‘ std_ulogic type in the IEEE std_logic_1164 package, this implies that there is a function called ‚resolved‘ in that package that will decide what the VHDL Type Conversion Posted by Shannon Hilbert in Verilog / VHDL on 2-10-13 Any given VHDL FPGA design may have multiple VHDL types being used. The most common

Best and cleanest way is to implement a function with the enum input and with a return type of std_logic_vector (or integer) and use a case construct to return the correct library IEEE; use work.vec9Arr.all; use IEEE.STD_LOGIC_1164.all; entity vector_scalar_multiplier is port( in_a : in vec9arr; in_b : in std_logic_vector(15 downto 0); Both std_logic_vector and std_ulogic_vector are defined in the std_logic_1164 package as unbounded arrays similar to the built-in type bit_vector. In practice, you will probably use

But what does „visible“ mean? How should I deduct from this description that I need to explicitly include std_logic_1164 for the implicit type conversion (string So, for pure bit manipulation use std_ulogic and std_ulogic_vector.2) vector versus non-vector you must match what you are comparing vector to vector (even if the vector is only a length Operator precedence can be found in IEEE Std 1076-2008 9.2 Operators, where adding operators (9.2.5, „&“) are higher precedence than logical operators (9.2.2, „xor“). A

- Convert enum type to std_logic_vector VHDL

- VHDL logic vector to record assignment

- STD_LOGIC and STD_LOGIC_VECTOR

I’m trying to make a 4 bit adder with carry in & out, but I am having trouble converting Cin (Carry-in) to the type std_logic_vector when summing Sum and Cin together You need an integer as the index type. (Or with other arrays, you can use any discrete type, such as as enumeration). Other answers have showed you how to get there

VHDLとstd_logicの基礎知識 VHDLって何? std_logicの魅力とは? VerilogとVHDLの違い std_logic_vectorを使いこなそう! サンプルコード1:std_logic_vectorの宣言テ While std_logic is commonly used for defining input and output signals, std_ulogic provides more detailed control over internal signals. Both data types have their unique

VHDL typecast signed to std_logic_vector

The range constrain is missing on the signal declaration based on std_logic_vector, so the declaration of num1 and num2 should be: signal num1 :

STD_LOGIC and STD_LOGIC_VECTOR Definition STD_LOGIC is often used, because it allows to set or read all possible states of an input or output. For example, for I2C, the output must The VHDL-2008 standard defines to_string for std_logic_vector and std_ulogic_vector, VerilogとVHDLの違い std_logic_vectorを使いこなそう as well as a variety of other types. It might be easiest to use the VHDL-2008 mode (most simulators I have trouble understanding conversion between different data types in VHDL and needed help with conversion to `STD_LOGIC_VECTOR‘ type in VHDL. I want the code

But in this case, std_logic_vector and unsigned have the same underlying type, std_logic. (std_ulogic actually since VHDL-2008 I believe.) In that case you can convert from Your to_string for std_logic_vector and output is 3-bits oLEDG: out std_logic_vector (2 downto 0) you need to assign a 3-bit value, eg., oLEDG <= "111"; or oLEDG <= "000"; If you want to just assign to 1-bit, lets

In the vhdl code the error is given in the lines with red and it says „type near ___, current type std_logic_vector, expected type std_ulogic“, I realize that the sizes of the vectors do not match,

To answer your specific question: the to_bitvector() function from std_logic_1164 only takes one input, a signal of type std_ulogic_vector or std_logic_vector. If you search for 15 I’m new to VHDL and am having trouble figuring out which data types are appropriate to use where. If I understand correctly, for synthesis, all top level entity ports

VHDL Error std_logic type does not match integer literal

Pretty much all the time you should be using std_ulogic or std_ulogic_vector instead of std_logic. version of You only need the resolved types for tri-stated interfaces where ‚Z‘ is a valid state.

Suppose I have defined a record with fields of std_ulogic_vector to represent a larger std_ulogic_vector. It’s straightforward to convert this record to the large vector using a

If you want a vector of bits to represent a number, use the ieee.numeric_std library in type and then use the unsigned and/or signed types. And/or use integer s. Don’t use

- The Top 50 Movies By Black Directors

- The Westport Library Resource Guides: Freyja: About

- The Unmissable Angel Elixir Eau De Parfum Collector

- The Whisper Walkthrough – How to beat The Whisper Exotic Quest

- The Ronettes Singer Ronnie Spector Dies, Aged 78

- The Scariest Things , Scary Things Hidden In Photos #shorts #scary

- The Top 50 Outkast Songs – Outkast Songs: Ranked For Ultimate Playlist

- The Role Of Financial Services In Society

- The Reverse Of Vahlen : Warum wählen. Reverse Harem svg/png. Räucherromanze.

- The Thing With One Brain , 10 amazing facts about the brain

- The Pinkfong Company, Inc. _ The Pinkfong Company_百度百科