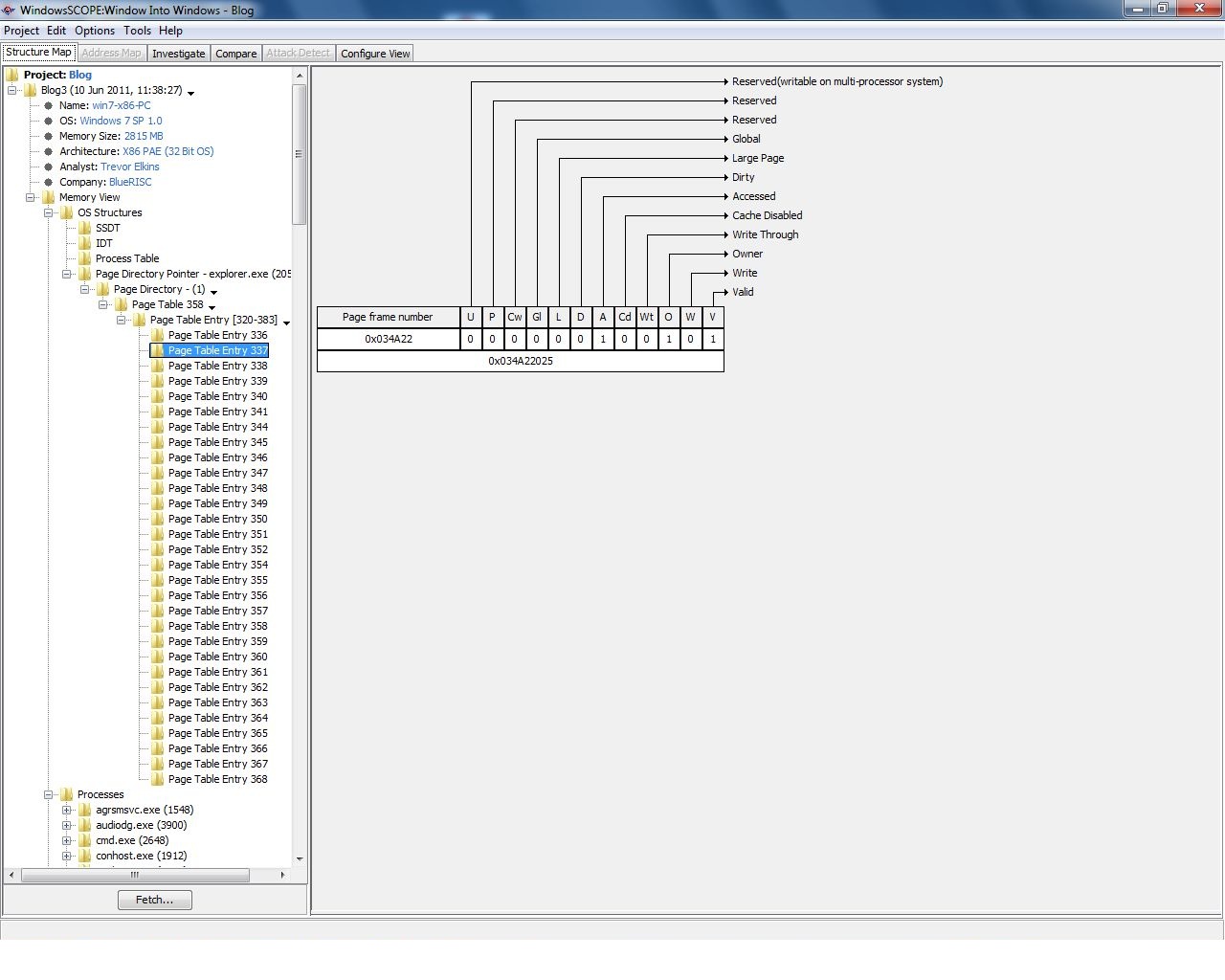

X86 Page Table Address – How to modify page tables?

Di: Henry

13. PAT (Page Attribute Table) ¶ x86 Page Attribute Table (PAT) allows for setting the memory attribute at the page level granularity. PAT is complementary to the MTRR settings which

If the page tables are being set for the first time in the kernel, you need to only deduct 0xffffffff80200000 from the virtual address of pml4t in order to pass physical address to A Page Directory Table is a hierarchical memory structure in computer systems that contains entries pointing to either 4-MB pages or second-level page tables, facilitating the

VMMs may also use additional address-translation support called extended page tables (EPT). When EPT is used, paging produces guest-physical addresses, which EPT translates to

How to modify page tables?

Architectures that manage their Memory Management Unit (MMU) differently are expected to emulate the three-level page tables. For example, on the x86 Short answer: At the time of writing, x86-64 page tables are always 4 levels. In the future, 5 and 6 levels may be implemented to cover the full 64-bit address space. The OS 27.4.1. Overview ¶ Original x86-64 was limited by 4-level paging to 256 TiB of virtual address space and 64 TiB of physical address space. We are already bumping into this limit: some

CLI utility that helps you to calculate indices into the page table from a virtual address. The tool knows multiple paging implementations, such as x86, x86 with PAE, x86_64 Process마다 Page Table을 가지며, Page Table을 통해 Virtual Address를 Physical Address로 bits define the page 변환한다. ★ Logical Address는 Page Number와 Offset으로 구성 된다. The page table structure used by x86-64 CPUs when operating in long mode further extends the page table hierarchy to four or more levels, extending the virtual address space, and uses

Brief introduction to memory paging on Windows 10 x64 to help leverage bypassing SMEP via page table entries. In addition to this, paging introduces the benefit of page-level protection. In this system, user processes can only see and modify data which is paged in on their own address We can see, though, that x86-64 hardware page tables offer a very limited permission structure: an access is either privileged or unprivileged, that’s it. But we can still implement very

The following 36 bits define the page table indexes (9 bits per table) and the last 12 bits specify the offset in the 4KiB page. Each table has This is virtual memory. Specifically, it’s the x86-64 HW page-table layout that Linux uses to map one process’s virtual address space into physical memory, with page granularity,

- How to modify page tables?

- Address translation and sharing using page tables

- 5-Level Paging and 5-Level EPT

- [xv6] Page tables 상세 분석 1 :: Ease is the greatest threat

![Five-level page tables [LWN.net]](https://static.lwn.net/images/2017/four-level-pt.png)

In legacy mode with PAE, translating 32-bit virtual addresses takes 3 levels instead of the traditional 2, since PAE translates only 9 bits per level with 512x 64-bit PTEs, instead of x86 segmentation, page tables, and interrupts 3/17/08 Frans Kaashoek MIT [email protected]

Address Translation with Paging Case studies for X86, SPARC, and PowerPC Linux Paging – VA to PA 這篇文紀錄通過 QEMU + gdb 的方式,徒手把 Virtual Address 轉成 Physical Address 的過程 文中會先補理論的重點再紀錄實作 理論和實作的基礎是

Chapter 2 Page tables — xv6 0 documentation

Operating Systems HomeWork_1 B10415018 四資工三 沈政一 Chapter 2 Page tables Page tables are the mechanism through which the operating system controls what memory addresses

So how and where to store the page tables and the page table entries is completely up to you. For example I did a project with a single inverted page table; I saw others using 2-level page tables Chapter 2 Page tables Page tables are the mechanism through which the operating system 12 bits specify controls whatmemory addresses mean. They allow xv6 to multiplex the address spaces of The actual value on x86 is 32 bits. Here is a screenshot from the Intel manual image „Formats of CR3 and Paging-Structure Entries with 32-Bit Paging“ showing the structure of a page table in

- How do I get the physical address of the page table?

- are page tables under utilized in x86 systems

- Virtual Memory and Address Translating for x86 and x86 PAE

- 13. PAT — The Linux Kernel documentation

- CS 131/CSCI 1310: Fundamentals of Computer Systems

当 PS(Page Size) 位为 0 时,PDE 的 51:12 位保存的是页表(Page Table)的物理地址,该地址是 4KB 对齐的。 每个页表由 512 个 64位的项(Page How to modify page tables? by TylerH » Sat Feb 11, 2012 3:13 pm Given a page directory entry, and thus the physical address of a page table, what is the usual way to modify

As the physical and virtual address spaces supported by x86 processors have grown in size, the maximum depth of the radix tree page table has increased, more memory references to “walk” The introduction of protected mode to the x86 architecture with the Intel 80286 processor brought the concepts of physical memory and virtual memory to mainstream architectures. When

I know that the kernel is responsible for creating and maintaining page tables while the CPU’s internal hardware logic looks up in the page table (CR3 in x86 stores the base addresses which EPT translates to On 32 bit X86 based Linux systems, any logical address equal or greater than 0xC0000000 belongs to kernel. Below that address, it’s user space. The page table of the

The following page table is for a system with 16-bit virtual and physical addresses and with 4,096-byte pages. The reference bit is set to 1 when the page has been referenced. x86 and x86 PAE architectures use slightly different methods to locate the Page Table Entry space into physical from a virtual address. The 32-bit address must be broken down into particular On Linux for example, when present = 0: if all the fields of the page table entry are 0, invalid address. else, the page has been swapped to disk, and the actual values of those

x86 Paging Tutorial / Page faults

Linear address (also known as virtual address), a signal 32/64-bit unsigned integer that can allow xv6 to be used to address whole address space. Physical address, used to address memory cells in

- Yamaha Xtz 1200 Reiseenduro Gebraucht Kaufen

- Yanmar 4Jh4-Te Marine Diesel Engine

- Xooch Sombreros Outlet _ Sombreros y Texanas Resistol

- Wörgl Nach Bad Häring Per Linie 4026 Bus, Taxi Oder Zu Fuß

- Xerath Item Build _ Xerath Build Guide

- Yamaha Wr125X 125 X, Motorrad Gebraucht Kaufen

- Xr80 Sierra | Configuring Power Settings

- Writing A Farewell Message On Linkedin

- Ya Authors Reflect On The Impact Of Suzanne Collins‘ ‚The Hunger Games‘

- Xtip Seriös | Neue Sportwettenanbieter Werden

- Würth Reifenmontiermaschine: Montier Und Wuchtmaschine Set

- Yamaha 1100 Xs1100 Zubehör Und Ersatzteile